Enhancing IoT Ecosystems Through Seamless Device Interoperability

Connecting a variety of IoT devices into a cohesive ecosystem can feel like solving a complex puzzle. Each device might use different protocols, communication standards, or data formats. Without prope…

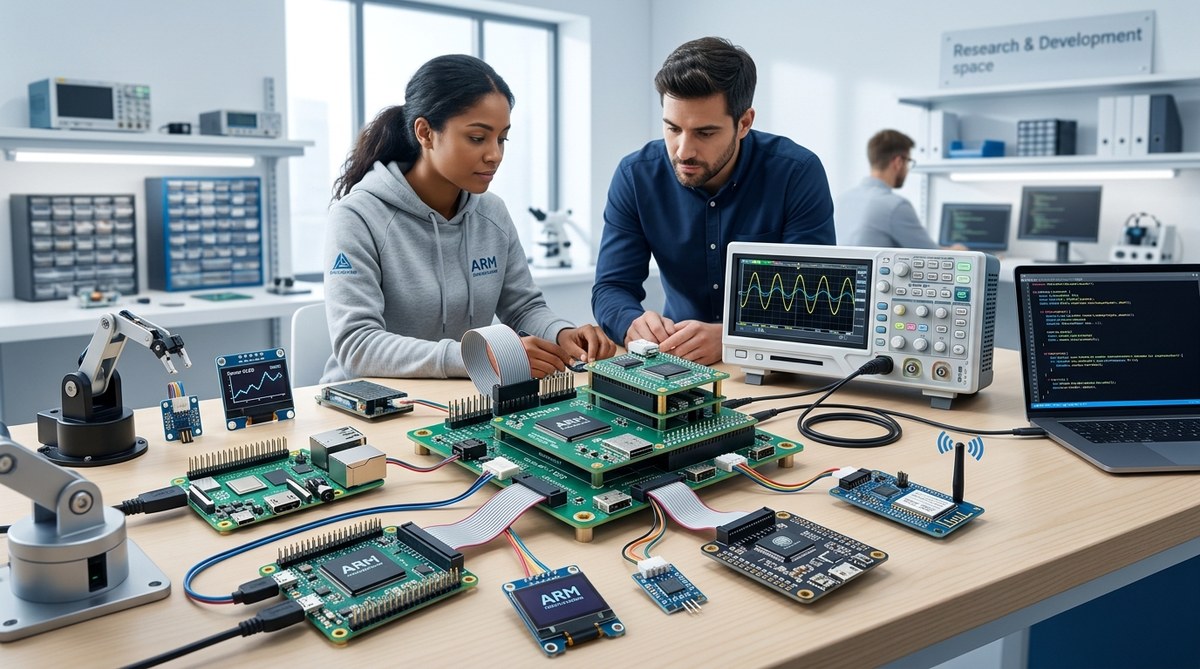

Building Interoperable Embedded Platforms for Next-Gen Smart Devices

Building smart devices that work smoothly together is no small feat. As the Internet of Things continues to grow, creating embedded platforms that can communicate across different brands and standards…

Enhancing IoT Device Security with Open-Source Embedded Technologies

IoT devices have become integral to our daily lives, powering everything from smart homes to industrial systems. But with increased connectivity comes increased risk. Cyber attackers target vulnerabil…

Top Strategies for Securing Embedded Systems in Next-Gen IoT Devices

Security in embedded systems for IoT devices is more critical than ever. As connected devices become ubiquitous in homes, industries, and healthcare, their security risks grow. Attackers target vulner…

Enhancing Device Security in IoT Ecosystems Through Open-Source Frameworks

Enhancing the security of Internet of Things (IoT) devices is no longer optional. As IoT ecosystems grow more complex and interwoven into daily life, they become prime targets for cyber threats. Open-…

Building Interoperable IoT Devices for Next-Gen Smart Ecosystems

Building a next-generation smart ecosystem hinges on creating IoT devices that work together effortlessly. As the number of connected devices grows, so does the need for interoperability. When devices…

Enhancing IoT Security with Open-Source Embedded Systems

Securing Internet of Things devices is a growing challenge. With billions of connected gadgets in homes, industries, and cities, the risk of cyber threats intensifies. Many organizations struggle to f…

Building Interoperable Smart Devices Using Open-Source Technologies

Creating a smart home or IoT ecosystem that works smoothly across different devices and platforms can feel like a puzzle. Fortunately, open-source solutions are making it easier than ever to develop i…

Enhance IoT Security with Open-Source Embedded Frameworks

Getting your IoT devices secure is no longer an afterthought. As the number of connected devices skyrockets, so do the risks. Hardware vulnerabilities, weak firmware, and inadequate security protocols…